目次

皆さんこんにちは。吉村(@alterakey)です。ATLでFPGAの調査をしています。

高位合成とOpenCL

前稿で解説したように、FPGA開発は低レイヤーの設計を伴ないます。そのためFPGA開発はプロセッサを使う開発と比べて敷居が高いものでした。

ところが最近になって高位合成という手法が利用できるようになってきました。高位合成とはアルゴリズムの実装から、低レイヤー設計を自動的に生成する手法です。低レイヤー設計が自動的に生成されることで、開発者がFPGAにアルゴリズムを実装しやすくなります。

高位合成を行なう手段にOpenCLがあります。OpenCLとはKhronosグループが標準化を進める並列計算ライブラリです。OpenCLを使うと環境に依存せずに計算(カーネル)を並列実行できます。カーネルが環境に依存しないとは、カーネルを実行するものが何であるかを問わず共通に書けることを指します。カーネルはOpenCL Cという言語で記述します。OpenCL CはC99にOpenCL独自の拡張を施した言語です。

Note

OpenCLについて詳しくは 公式ページ をご参照ください。

OpenCLを使う高位合成では、FPGAチップはOpenCLから使える計算装置(デバイス)として構成されます。計算する時には、システム(ホスト)からOpenCLを使用してデバイスを駆動します。

開発環境

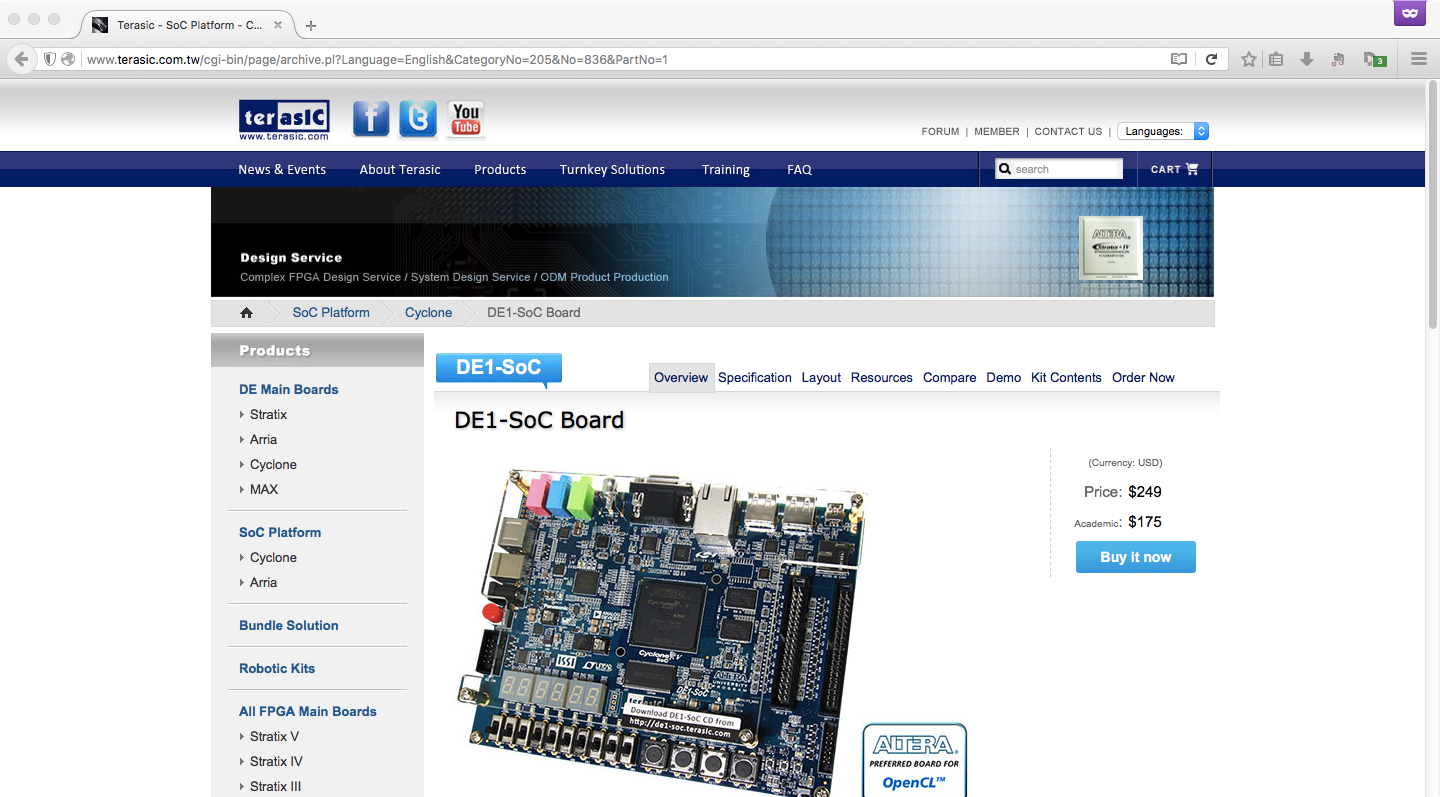

高位合成を用いるには専用の開発環境(高位合成環境)が必要です。高位合成環境はFPGAおよびボードによって異なります。ボードとはチップと周辺機器を搭載する基板です。本稿で使うFPGAはAltera社のCyclone V SoCです。ボードにはDE1-SoC(Terasic社)を使用します。

Altera社の高位合成環境は、高位合成SDK・BSPの2つで構成されます。高位合成SDKとは高位合成環境に必要な開発ツールをまとめたパッケージです。BSPとはボードごとに異なるファイル群で、高位合成SDKにインストールして使います。以下、解説します。

またWindows環境でAltera社の高位合成環境を使うためには、上の2つをインストールに加えてさらに2つの手順(Unix風環境の設定・クロスコンパイル環境の設定)が必要です。Unix風環境とは、Windows上でUnix系ツールを使うための環境です。本稿で使う環境は MSYS2 です。クロスコンパイル環境とは、ホスト側プログラムをビルドする環境です。追って解説します。

Note

開発環境のライセンス設定について本稿では触れません。詳しくは インストールおよびライセンス・マニュアルをご参照ください。

高位合成SDKのインストール

高位合成SDKはAltera社から入手します。高位合成SDKは有償です。

Note

高位合成SDKが無償試用できるかについては調査していません。

高位合成SDKを入手するにはAltera社に登録する必要があります。登録については 前稿をご参照ください。

登録が完了するとサポートポータル(My Altera)へアクセス可能になります。

My Alteraへログインし、下メニューから「Download Quartus II」を選択します。選択するとダウンロードセンターへ移動します。

Note

現在、Quartus IIの名称がQuartus Primeに変更されています。

移動したら下へスクロールし「Altera SDK for OpenCL」ボタンを選択します。

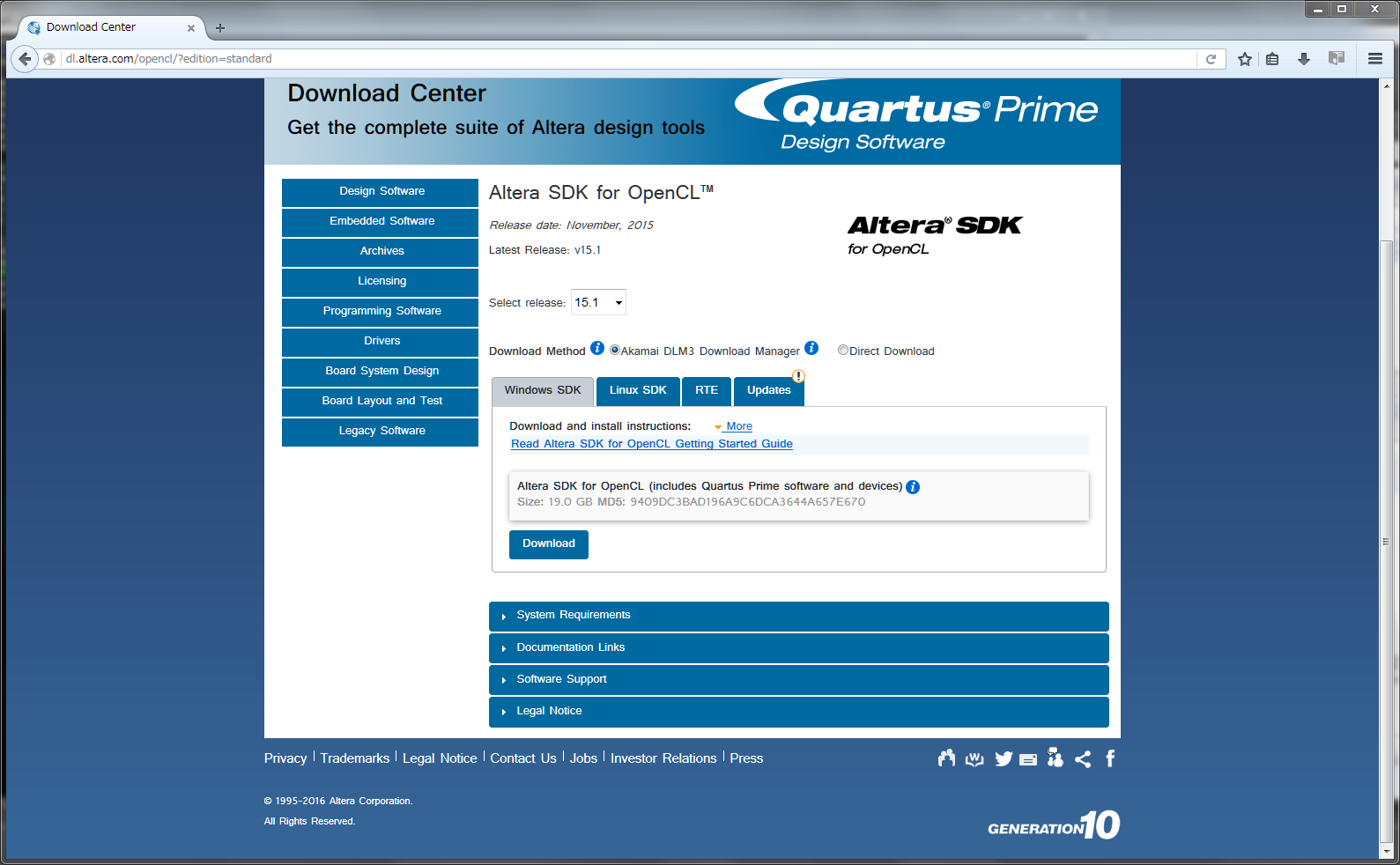

選択するとダウンロードの方法を選べます。ダウンロードの方法はダイレクトダウンロード・ダウンロードマネージャの2種類から選べます。ダウンロードマネージャを選ぶことをおすすめします。ダウンロードマネージャはダイレクトダウンロードに比べると、インストールの手間はかかりますがダウンロードがスムーズに行なえます。

次にダウンロードするイメージを選びます。ダウンロードできるイメージにはWindows SDK・Linux SDKがあります。本稿ではWindowsを使います。下にある「Download」ボタンを押してダウンロードを開始します。

ダウンロードしたらインストールします。インストールの手順は本稿では省略します。手順は アルテラ SDK for OpenCL スタート・ガイド をご参照ください。

BSPのインストール

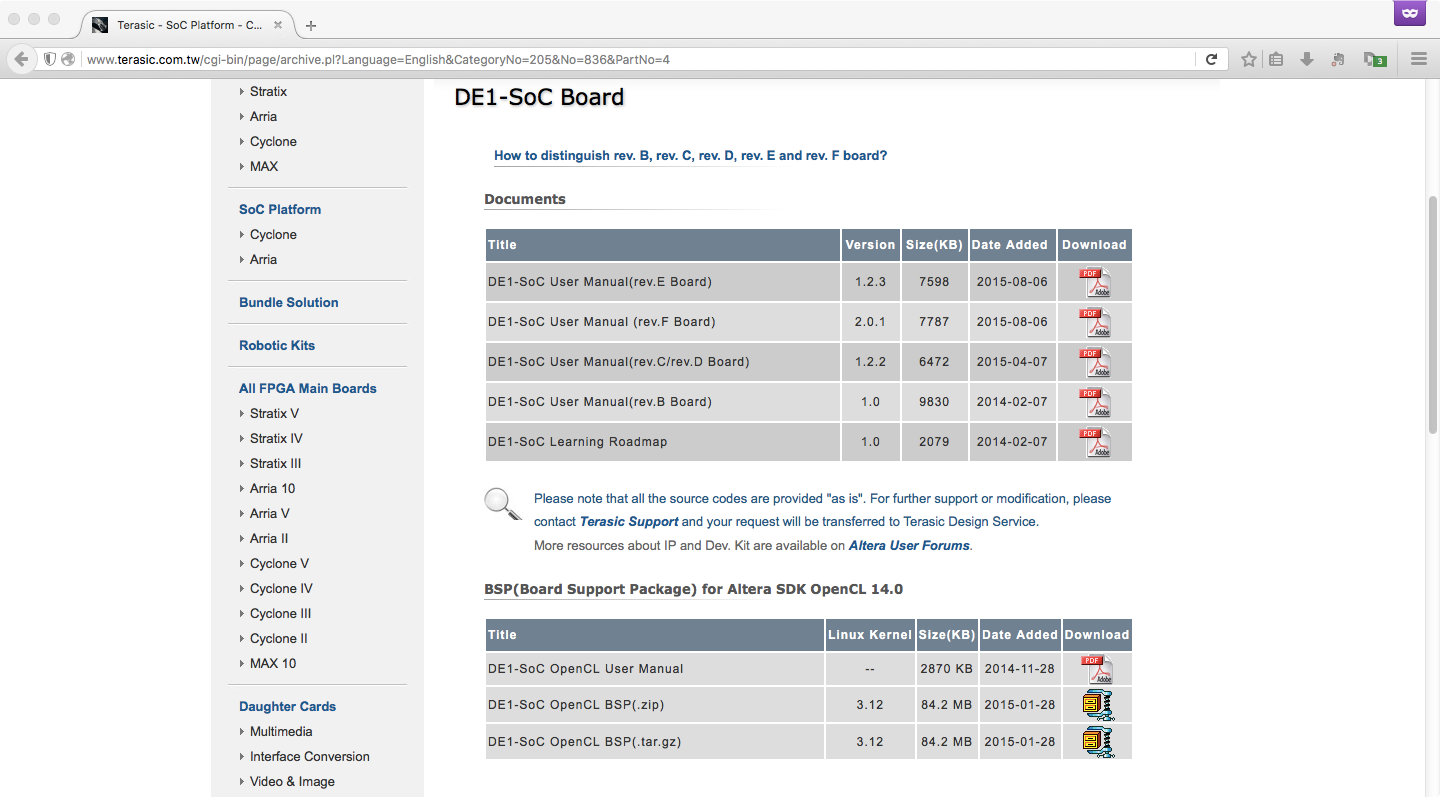

BSPは評価ボードメーカから入手します。本稿で使うDE1-SoCの場合、terasic社からダウンロードできます。

tearsic社の DE1-SoCに関するページ を表示します。

表示したページの右上メニューから[Resources]を選びダウンロードできる資料を表示します。BSPは「BSP(Board Support Package) for Altera SDK OpenCL 14.0」以下にある3つのファイルです。ダウンロードすべきファイルはユーザマニュアル・zipアーカイブです。

ダウンロードしたらインストールします。インストールの手順は本稿では省略します。手順は DE1-SoC OpenCL User Manual をご参照ください。

Unix風環境の設定

Unix風環境とは、Windows上でUnix系ツールを使うための環境です。 前稿ではAltera社のFPGA開発環境は統合開発環境だと解説しました。しかし、高位合成を使う場合は統合開発環境は使えません。高位合成系がまだ統合開発環境へ対応していないためです。また高位合成系はUnix系の文化に従っています。そのためWindows環境で高位合成を行なうにはUnix風環境を準備する必要があります。

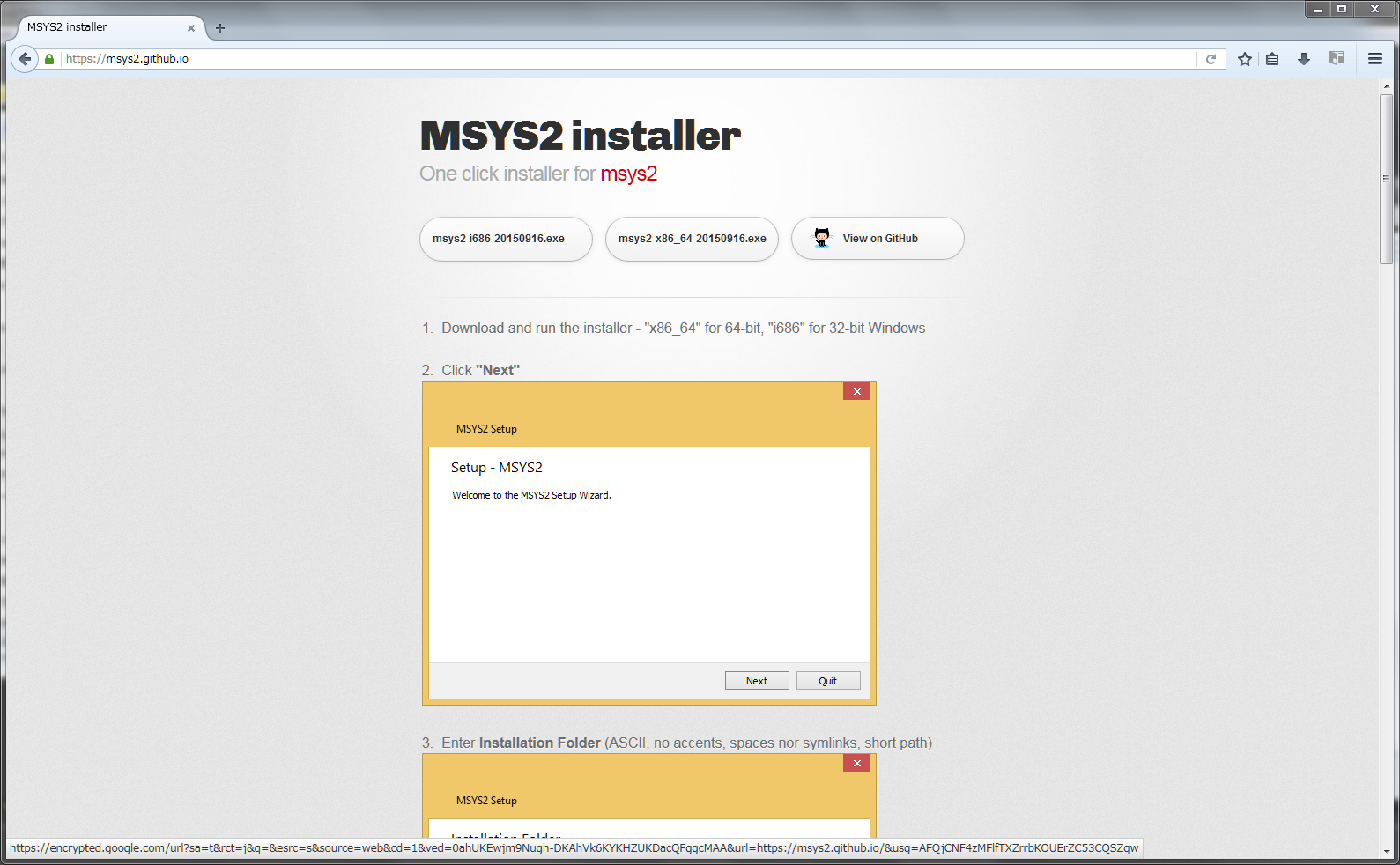

本稿で使うUnix風環境は MSYS2 です。MSYS2はGit for Windowsの動作基盤にも採用されている、比較的軽量なUnix風環境です。

MSYS2は 公式ページ からダウンロードできます。ダウンロードしたらインストールします。インストール手順は本稿では省略します。手順は MSYS2の公式ページ をご参照ください。

次にMSYS2のシェルに開発環境へのパスを通します。開発環境へのパスを通すにはMSYS2を起動し、以下のコマンドを実行します。コマンドの実行後、シェルを再起動すると反映されます。

$ echo 'export PATH=/c/altera/15.0/hld/bin:$PATH' >> ~/.profile

クロスコンパイル環境の設定

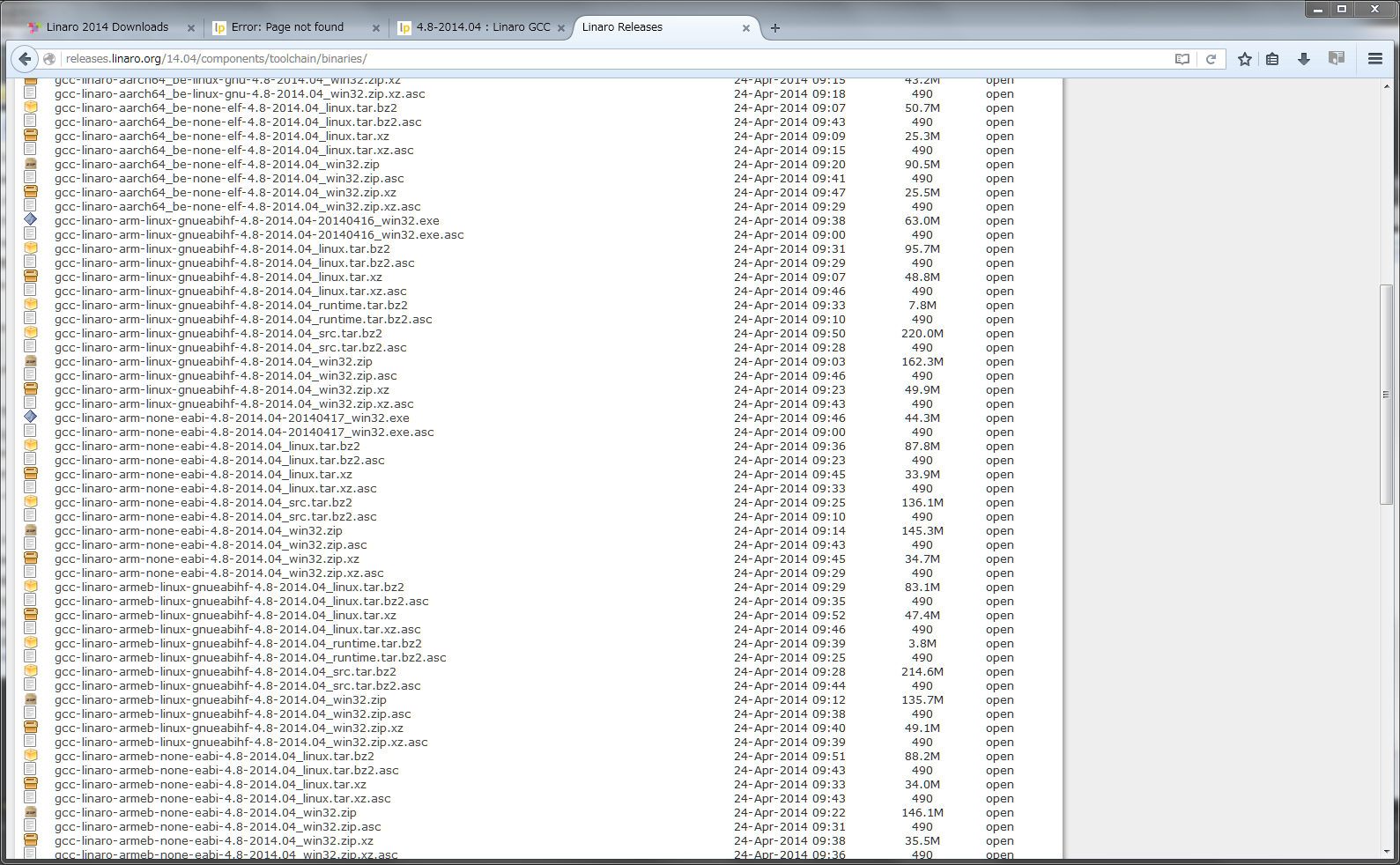

クロスコンパイル環境とは、ホスト側プログラムをビルドする環境です。本稿で使うクロスコンパイル環境はgcc-linaro-arm-linux-gnueabihf-4.8-2014.04です。gcc-linaro-arm-linux-gnueabihf-4.8-2014.04は、Linaro 14.04にlinaro-toolchain-binaries 4.8の一部として収録されています。

gcc-linaro-arm-linux-gnueabihf-4.8-2014.04(以下クロスコンパイル環境)を linaro-toolchain-binaries 4.8のリリースページ からダウンロードします。本稿ではWindows環境を使いますので、ダウンロードすべきファイルは gcc-linaro-arm-linux-gnueabihf-4.8-2014.04_win32.zip になります。

ダウンロードしたらインストールします。インストールするにはファイルを適当なディレクトリに展開します。

続けてMSYS2のシェルにクロスコンパイル環境へのパスを通します。クロスコンパイル環境へのパスを通すにはMSYS2を起動し、コマンドを実行します。以下はパスを通すコマンドの例です。例では、クロスコンパイル環境をC:\Users\taky\bin\gcc-linaro-arm-linux-gnueabihf-4.8-2014.04_win32へ展開したと仮定しています。コマンドの実行後、シェルを再起動すると反映されます。

$ echo 'export PATH=/c/Users/taky/bin/gcc-linaro-arm-linux-gnueabihf-4.8-2014.04_win32/bin:$PATH' >> ~/.profile

ボードの初期設定

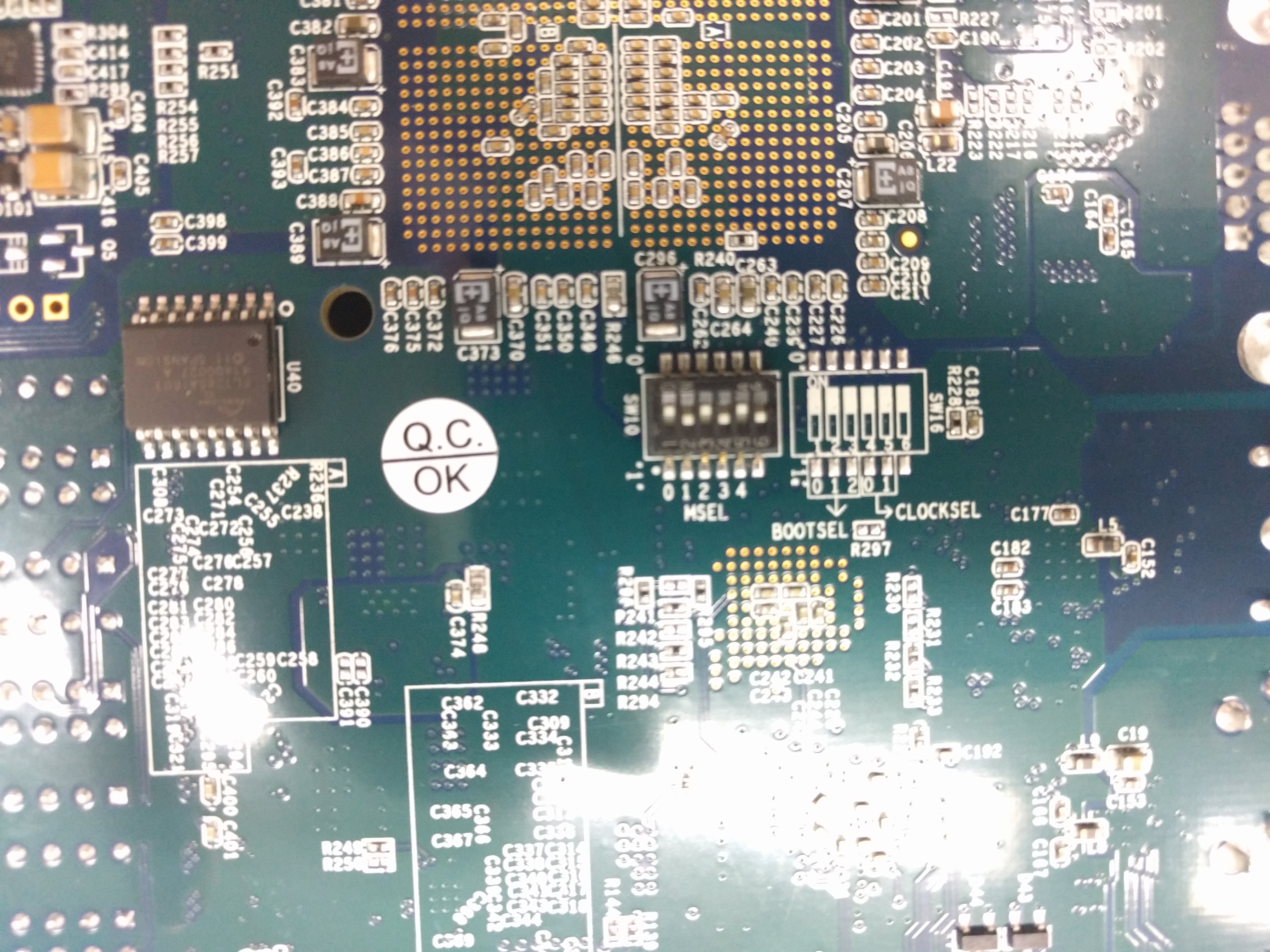

本稿で使用するDE1-SoCの場合、高位合成を使う場合には違う初期設定が必要です。高位合成を使う場合の初期設定は、DIPスイッチの設定とホスト起動用SDカード(ブートカード)の作成の2つです。

DIPスイッチの設定はボードを高位合成評価用に設定するステップです。DE1-SoCではMSELを設定する必要があります。MSELは基板の裏にある小さなDIPスイッチです。MSEL4〜0をON・OFF・ON・OFF・ON(01010)に設定します。

ブートカードの作成には4GB以上の容量を持つSDカードが必要です。用意したSDカードに Win32 Disk Imager を使ってホスト起動用イメージファイルを書き込みます。ホスト起動用イメージファイルはBSPをインストールすると作られます。本稿ではC:\altera\15.0\hld\board\de1soc\linux_sd_card_image.imgにあります。

ブートカードをボードに挿入し立ち上げてみましょう。起動用イメージファイルはシリアルコンソールが有効になっています。シリアルコンソールとはシリアルポート経由で制御できるホストの機能です。シリアルコンソールに接続するには2つの手順が必要です。まずDE1-SoCのUSBシリアルポートと開発マシンをUSBケーブルでつなぎます。そしてTeraTermなどのターミナルソフトを使用してUSBシリアルポートへ接続します。接続に必要なシリアルポートの設定は以下のとおりです。

| ボーレート |

115200 |

|

データビット |

8ビット |

|

パリティ |

なし |

|

ストップビット |

1ビット |

Note

USBシリアルポートドライバは http://www.ftdichip.com/Drivers/VCP.htm からもダウンロードできます。

接続に成功するとホストの起動とともにシステムログが流れます。最後にログインプロンプトが現われます。以下はログインプロンプトの例です。

|

1 2 3 4 |

Poky 8.0 (Yocto Project 1.3 Reference Distro) 1.3 socfpga ttyS0 socfpga login: |

ユーザ名rootで入れることを確認します。

初期設定は以上です。

サンプル

では高位合成を用いてFPGA開発を行なってみます。本稿で使うサンプルプロジェクト(サンプル)は https://bitbucket.org/taky/fpga-hld-sample にあります。本稿のサンプルを実行すると、hello worldという文字列をコンソールに書き出します。

以下はサンプルで使うOpenCLカーネルのソースコードです。実行すると出力バッファにhello worldの文字列を書き出します。

サンプルのOpenCLカーネル (device/hello_world.cl).

|

1 2 3 4 5 6 7 |

__constant char hw[] = "hello world\n"; __kernel void hello(__global char *out) { int tid = get_global_id(0); out[tid] = hw[tid]; } |

サンプルの動作にはビルド・転送・実行の3つの手順が必要です。

ビルド

最初にビルドします。ビルド対象は2つ(ホスト側プログラム・デバイス側フロー)あります。ビルドするには両者ともMSYS2にコマンドを打ち込みます。

まずホスト側プログラムのビルドをします。ビルドに必要なコマンドは以下です。

|

1 2 |

$ make host |

次にデバイス側フローのビルドをします。ビルドに必要なコマンドは以下です。

|

1 2 |

$ make device |

Note

デバイス側フローのビルドには長い時間がかかります。本稿のサンプルの場合、デバイス側フローのビルドにかかる時間の目安はCore i7 4790で15分程度です。

ブートカードにおける構成ファイルの設定

実は動作させるにはもう一つだけ必要な設定があります。それはブートカードにおける構成ファイルの設定です。構成ファイルの設定は一度だけ行ないます。

設定すべき構成ファイルはブートカード内の/opencl.rbfです。構成ファイルを設定するには、デバイス側フローのビルドで作成されたディレクトリ内にあるtop.rbfファイルで構成ファイルを上書きます。デバイス側フローをビルドすると、aocxファイル(フローファイル)と同じ場所に、フローファイルと同名でディレクトリが作成されます。

以下は上書きに使うコマンドの例です。例では2つの事柄を仮定しています。1つ目はサンプルがC:\Users\taky\works\fpga\hello_worldにあることです。そして2つ目はブートカードがGドライブにあることです。

|

1 2 |

$ cp /c/Users/taky/works/fpga/hello_world/build/hello_world/top.rbf /g/opencl.rbf |

以上でブートカードにおける構成ファイルの設定は完了です。

転送

転送はscpコマンドで行ないます。scpコマンドとはファイルやディレクトリを安全に転送するコマンドです。

ホストにscpコマンドで転送するにあたって、ホストのIPアドレスを把握する必要があります。ボードのIPアドレスを把握するにはホストを起動します。ホストを起動するにはブートカードをボードに挿入し、USBシリアルポートおよびEthernetを接続して電源を投入します。ホストが起動したら、シリアルコンソールからrootでログインします。ログインしたらIPアドレスを調べます。IPアドレスを把握するにはifconfigコマンドを使用します。以下はコマンドの実行例です。例のeth0はEthernetインターフェース名です。

|

1 2 3 4 5 |

# ifconfig eth0 eth0 Link encap:Ethernet HWaddr XX:XX:XX:XX:XX:XX inet addr:192.168.100.16 Bcast:192.168.100.255 Mask:255.255.255.0 ... |

inet addr:の次に記載されているアドレス(例では192.168.100.16)がIPアドレスです。

IPアドレスを把握したら、scpで転送します。転送すべきファイルはホスト側実行ファイル・デバイス側フローファイルの2つです。以下は転送に使うコマンドの例です。例ではホストのIPアドレスが192.168.100.16であると仮定しています。

|

1 2 |

$ scp build/hello build/hello_world.aocx root@192.168.100.16:. |

起動

転送したサンプルを起動するには2つの手順(OpenCL環境の初期化・実行)が必要です。

OpenCL環境を初期化するには、まずrootでログインします。ログイン後、以下のコマンドを打ち込みます。

|

1 2 |

# source ./init_opencl.sh |

Note

初期化はログインの度に行なう必要があります。

実行するにはホスト側実行ファイルを実行します。本稿のサンプルでは、起動するコマンドは./helloです。以下は実行結果の例です。

|

1 2 3 4 |

# chmod u+x ./hello # ./hello hello world |

まとめ

本稿ではFPGAの高位合成を解説しました。高位合成とは最近出てきたFPGA開発手法です。高位合成では低レイヤーの設計が自動で行なわれるので、従来のFPGA開発手法に比べてアルゴリズム本体の実装がしやすい特徴があります。次に高位合成を行なう環境について触れました。Windows環境で高位合成を行なうには、Altera社の開発環境のインストール以外にUnix風環境やクロスコンパイル環境を入れる必要がありました。最後に整備した開発環境でサンプルを高位合成し、動作させました。

本稿では長さの関係上、サンプルの詳細なソースコードには触れられませんでした。サンプルのソースコードを見ていただくと、一般的なOpenCLプログラムと似た構造が見て取れると思います。特にOpenCLカーネルのソースコードを見ていただくと、見なれた形でアルゴリズムが記述されていることを見ていただけると思います。

次回は高位合成の応用について扱います。それではまた。